4. HS-Signalübertragung in der Praxis - Zusammenfassung

Autoren: Sebastian Kollinger, Markus Huber, Michael Flint, Helmut Perschon, Guenes Alparslan

Dies ist eine Zusammenfassung des 4. Kapitels des FED-Leitfadens zum High-Speed-Baugruppen-Design. FED-Mitglieder können über die Kapitelübersicht auf den vollständigen Inhalt des Leitfadens zugreifen.

Vor dem Layoutstart müssen Design Guides und Application Notes gelesen werden (-> 1.8). Die Platzierung der Bauteile und die Fanout-/Via-Planung des BGA mit dem engsten, komplexesten Pitch definiert in Verbindung mit den erforderlichen Impedanzen und Spannungsversorgungen die Aufbau-Technologie (Standard/HDI). Daraus wird ein voraussichtlich geeigneter Lagenaufbau (Stackup) erstellt (-> 1.1 und -> 2.6). Unklare Fragen werden durch Prelayout-Simulationen sowie einem Austausch mit dem Anwendungstechniker („Field-Application-Engineer“) des Chipherstellers, geklärt oder anhand einer eigenen Layoutstudie untersucht (-> 1.9).

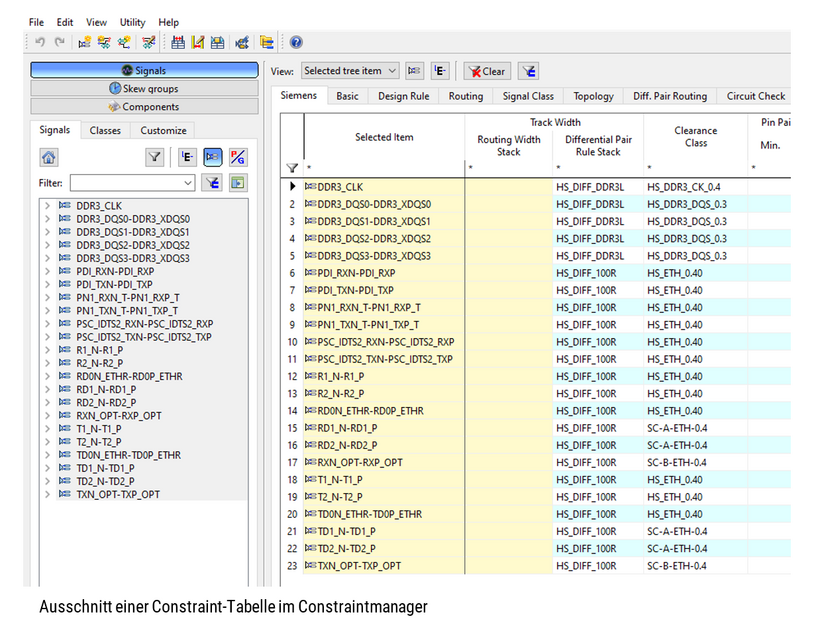

Jetzt können anhand der vorliegenden Designregeln für die kritischen Signale - dies sind i.d.R. die am schnellstens schaltenden - die Leitungstopologien (Leitungsführungen) als Vorgaben/Regeln in einem „Constraintmanager CM“ angelegt werden. Um einen schnellen Überblick über die verschiedenen Signale und Signalklassen zu gewinnen, sollte man die prinzipiellen HS-Interfaces schon auf Basis des Schaltplans mit Topologien (Verbindungsstrukturen) im Constraintmanager des EDA-Tools festlegen. Damit ist es möglich, kritischen Signalen ein regelbasiertes Routen vorzugeben.

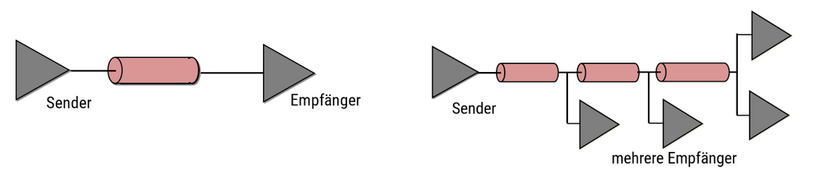

Als Verbindungsstrukturen kommen verschiedene Topologien zur Anwendung, die sich in der Art der Signalverteilung unterscheiden: Punkt zu Punkt (Sender direkt zum Empfänger), Punkt zu mehreren Punkten (als Kette: Fly-By /Daisy Chain) und schließlich Punkt zu 2-Punkt oder mehreren Punkten als Baumstruktur

Jede dieser Topologien hat unterschiedliche Anforderungen an die verschiedenen Streckenabschnitte: Leitungslänge, Impedanz, Skew, Crosstalk-Sensitivität, max. Dämpfung, Terminierungsvorgaben etc.

Constraintmanager

Um nicht den Überblick im Layouttool zu verlieren verwendet man sog. „Constraintmanager“ (CM): Statt manuell mit hohem Zeitaufwand jedem Signalabschnitt eines Signals einzeln im Layout bestimmte Teilbreiten oder Teillängen zu vergeben, werden die benötigten Informationen darüber tabellarisch im CM abgelegt. Dadurch können per Knopfdruck im LP-Layout die vorgegebenen HS-Regeln abgeprüft werden.

Über die „Annotation-Funktion“ des EDA-Tools gelangen die zugrunde legenden Informationen über die Topologien und deren Inhalte (Impedanz-Constraints, Längen-Constraints, Vias, Layer...) in das sog. Backend, also in das Layouttool. Eine manuelle Herangehensweise hat darüber hinaus noch den Nachteil, dass bei einem möglichen Redesign und Layouterwechsel nicht mehr klar wäre, nach welchen Regeln geroutet worden ist. Damit hat der Layoutdesigner im „CM“ des Layouttools eine Übersicht der Topologien und kann interaktiv beim Entflechten feststellen, ob die zugrundeliegenden Constraints wie Länge oder Breite des Signalweges beim Routing der Netze verletzt sind oder nicht.

Die Topologien erfordern unterschiedliche Terminierungsstrategien (-> 3.4) die bei den Simulationen der gelayouteten Leitungen erprobt werden. Sofern keine On-Die-Terminierung existiert, müssen externe Widerstände so gewählt werden, dass die Leitungsenden als Abschluss des Übertragungskanals den Wert der Leitungsimpedanz aufweisen. Leitungen, die deutlich kürzer als die kritische Leitungslänge sind (sog. Stubs), benötigen keine Terminierung.

Auslegung von DDR Memory Interfaces

Double Data Rate (DDR) Memory Interfaces findet man heute auf fast allen Baugruppen. Ein Memory Controller, integriert im Prozessor, ASIC oder FPGA, ist je nach gewünschtem Speicherausbau mit unterschiedlich vielen SDRAM Bausteinen verbunden. Aus dem DDR-Layout Design Guide geht die zu implementierende Netztopologie für die verschiedenen Signalgruppen hervor; ebenso die minimalen und maximalen Leitungslängen und der relative Skew sowie die maximal zulässige Anzahl von Vias je Verbindung und das zu verwendende Leiterplattenmaterial, um längenbasierte Dämpfungen einzuhalten..

Je nach Controllertyp werden das Taktsignal (CLK) sowie Adress-, Command- und Control-Signale unidirektional „Punkt zu Punkt“ oder „Punkt zu Multipunkt“ zu den SDRAM Input Pins einzeln übertragen. Die Clocks werden im Gegensatz zu den Adress- Command- und Control-Signalen differentiell geroutet. Beide Signalgruppen werden extern mit Widerständen auf der Leiterplatte abgeschlossen, um einwandfreie Signalintegrität zu gewährleisten. Als Verdrahtungsvarianten kommen „H-Tree“ (Baumstruktur, z.B. DDR1, DDR2) oder „Fly-By“ (z.B. DDR3, DDR4) zum Einsatz (-> 4.3)

Bei der Baumstruktur kommen die Signale an allen Takt-Input-Pins der SDRAMs innerhalb eines spezifizierten Skew an. Allerdings wird das vom Controller gesendete Signal bei einer hohen Anzahl von SDRAM (> 5) durch die Empfängereingänge kapazitiv sehr belastet, sodass sich die Flanken stark verschleifen und mögliche Reflexionen schwer zu kontrollieren sind. Dies schränkt die maximal mögliche Übertragungsrate ein.

Bei der Fly-By-Verdrahtung (Daisy-Chain; Kette) werden die SDRAM nacheinander angesteuert. Die Signale kommen an den SDRAM-Input Pins mit zeitlichem Versatz an. Der Controller kann diesen Zeitversatz ermitteln und bei der eigentlichen Datenübertragung und Auswertung berücksichtigen. Dazu läuft vorab bei der Initialisierung des Memory Interfaces ein Training ab. Vorteil der Verdrahtung ist die geringere kapazitive Belastung des Signals aufgrund der verteilten SDRAM Inputs und damit eine geringere Verschleifung der Signalflanken. Dies ermöglicht eine höhere Datenübertragungsrate als bei DDR1 oder DDR2.

Die Übertragung der Source-synchronen Daten- und Strobe-Signale erfolgt bidirektional Punkt-zu-Punkt. Die Strobe Signale, welche als Takt der Daten zu sehen sind, werden meist als differentielle Signale vorgesehen, während Daten- und Masksignale Single Ended ausgeführt sind. Fast alle Memory Controller und SDRAM besitzen interne „On Die Terminierungen“ (ODT), die für saubere Signale sowohl für WRITE als auch READ Commandos sorgen.

Beispiel einer Bus-Priority-Study

In allen Design-Guides für High-Speed Schnittstellen steht “routen sie die Signale so kurz und gut wie möglich“. Nur leider kann man das nicht für alle Signale gleichzeitig einhalten. Um sicherzustellen, dass man die richtigen Prioritäten setzt, sollte man eine „Bus Priority Study“ durchführen. Damit sieht man mit welchen Signalen man am besten anfängt, da man damit für diese Signale die meisten Freiheiten für das Routing hat.

Anhand eines konkreten Beispiels wird das Vorgehen erläutert (-> 4.4). Wenn man mit der falschen Platzierung oder das Routing mit den falschen Signalen beginnt, wird man nie ein optimales Layout erstellen können. Nur wenn man sich vorab überlegt, welche Signale die kritischsten sind und dies in einer Bus-Priority-Study bewertet, wird man am Ende die Schnittstellen auch bestmöglich routen können.

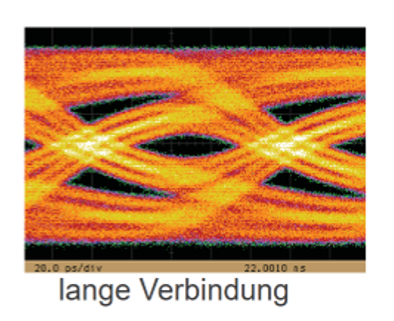

Längenbegrenzung des Übertragungskanals

Aufgrund der Signaldämpfung durch die Übertragungsleitung, die auch noch frequenzabhängig ist, wird das aus Grundfrequenz und Oberwellen zusammengesetzte Digitalsignal durch lange Leitungen ggf. derart verfälscht, dass eine zuverlässige Auswertung am Empfänger u.U. nicht mehr gegeben ist. Dabei werden vorrangig die hohen Frequenzen stark gedämpft, was eine Abflachung der Signalflanke zur Folge hat (-> 4.6 Augendiagramm).

Anhand des zulässigen Signaldämpfung in der Spec. (in dB/inch (bzw. dB/cm) kann bei bekanntem Verlustfaktor Df des Basismaterials sowie der Geometrie der Struktur vorab die Dämpfung pro Längeneinheit und damit eine maximale Länge ermittelt werden.

Falls eine größere Länge benötigt wird, müssen Zwischentreiber eingefügt werden. Sofern dies viele Leitungen betrifft und Zwischentreiber oder Kürzungen nicht möglich sind, bliebe nur verlustärmeres Material zu verwenden, um eine kritische Signalverschleifung als Folge zu starker Dämpfung der hohen Frequenzen zu vermeiden.

Crosstalk – Übersprechen

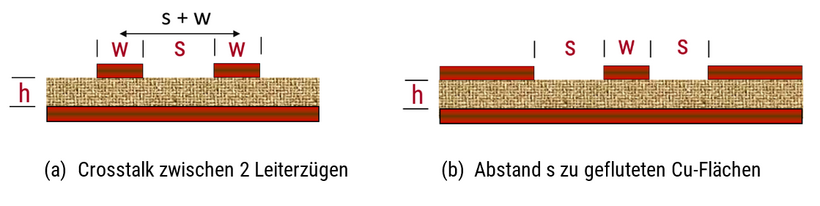

Verlaufen zwei oder mehrere Signalleiterbahnen über längere Strecken eng parallel, führt dies durch elektromagnetische Kopplung (kapazitiv und induktiv) zu unbeabsichtigter Übertragung von Energie aus einem Stromkreis in einen anderen. Kopplung erfolgt i.w. nur auf dicht benachbarte Leitungen über die sog. Koppelstrecke. Kopplung erfolgt nur, während sich Spannungen und Ströme auf der aktiven Leitung ändern. Die Impulsflanken sind daher entscheidend! Mit abnehmender Schaltzeit dt, also schnelleren Bauteilen, verstärken sich die überkoppelten Ströme und Spannungen.

Je geringer der Abstand der Leiterbahnen zur Referenzebene (je niedriger also die Impedanz) desto fester ist die Kopplung zur Potentiallage und desto geringer zur Nachbarleitung.

Als Abstandsempfehlung gilt die 3h-Regel: Beim Crosstalk s+w ≥ 3h und für sehr geringe Kopplung zu gefluteten Cu-Flächen (GND, VCC) s > 3h, um die Leitungsimpedanz nicht zu beeinflussen.

Near-End (NEXT) / Far-End (FEXT) Crosstalk

Die übergekoppelten Spannungen und Ströme verursachen nicht gewollte Amplitudenänderungen an den Leitungsenden der passiven Leitung, also sowohl auf der Einspeiseseite (Near-End) wie auch am empfangsseitigen Leitungsende (Far-End) die kritischen, störenden Signalpegel auf der inaktiven Leitung.

Layoutempfehlungen, um diese Effekte zu minimieren:

- Abstand zwischen den Leiterbahnen vergrößern

- Abstand zwischen Leiterbahn und Referenzebene möglichst klein machen

- Lötstopplack auf Außenlagen verwenden (geringerer FEXT) – am besten außen nur sehr langsame, statische Signale routen

- Stripline Routing anstatt Microstrip (geringerer FEXT)

- Differentiell routen

- Alle TX - Leitungen nebeneinander routen

- Alle RX - Leitungen nebeneinander routen

Mit Hilfe eines Fieldsolvers im CAD-Tool können die tatsächlichen Überkopplungen auch von beiden benachbarten Leiterzügen oder Kupferflächen ermittelt werden, also inwieweit das Layout ein geringes Übersprechen für ausreichend störungsarme Signalübertragung gewährleistet.