1. Übersicht

Autor: Hermann Ruckerbauer

Was muss ich im Vorfeld beachten - was erwartet mich?

Die Arbeit eines Designers beginnt lange bevor die erste Leitung/Verbindung gezogen oder die erste Plane gezeichnet wird. Um ein High Speed Design „first time right” zu machen ist es notwendig sich lange vor Beginn der Layoutarbeiten Gedanken über das Layout und Routing zu machen. Zum Aufwärmen hier vorab ein Überblick über die Themen und Aufgaben, die einen erwarten. Diese werden in den nachfolgenden Kapiteln ausführlich behandelt.

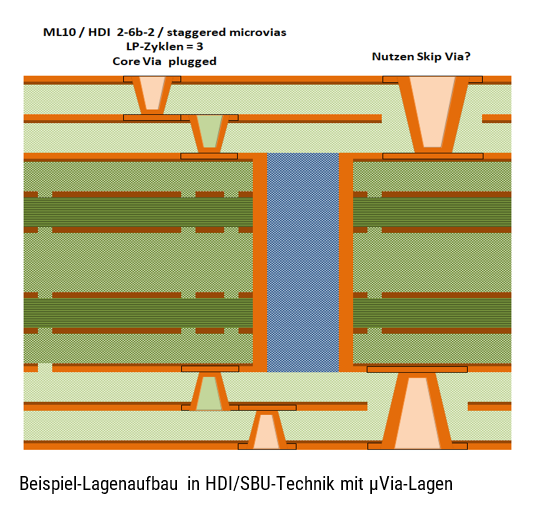

1.1. Definition eines Lagenaufbaus

Ein guter Startpunkt ist die Definition des Lagenaufbaus (Stackup). Dieser wird im nachfolgenden Kapitel 2 ausführlich behandelt. Deshalb soll an dieser Stelle der Hinweis reichen, dass man hierbei bereits festlegt:

- Welches ist das komplexeste Bauteil („Pinzahl/Pitch für Fanout“) und welche Leiterplattentechnologie wird hierfür benötigt (beidseitige SMD-Bestückung angenommen)

- Welche minimale, kostengünstige LB-Breite (L/S) ist nötig für ein effektives Fanout?

- Auf welchen Lagen wird das High Speed Routing gemacht.

- Auf welchen Lagen liegen die Power Supply Flächen

- Welches digital/analog GND/Masse Konzept muss implementiert werden

- Welche Via Technologie braucht man, um Via-Stubs zu vermeiden

- Welches PCB-Material ist für den geplanten Anwendungszweck am besten geeignet

Hier gibt es noch einige Punkte mehr zu berücksichtigen:

- Spec anschauen, Vorgaben, Design-Guides. Bei widersprüchlichen Vorgaben Rücksprache mit Entwickler nehmen. Dabei selber denken, nicht nur Vorgaben umsetzen; zumindest Vorgaben hinterfragen.

- Vergleichbare Designs von Anbietern anschauen; Interfaces beachten, Flächenabschätzung für das Routing. „Ausprobieren“ - Spec-Schaltungen sind immer nur suboptimale Lösungen.

- „Löse nur Probleme die du hast“ (z.B. sind kurze Verbindungen auch ohne Impedanz möglich, etc.)

Wenn diese Tätigkeiten nicht vor dem Layout erfolgen, wird das später im Designzyklus zu unliebsamen Überraschungen führen.

1.2. Platzierung

Durch geschicktes Platzieren von Steckern und Bauteilen kann man sich nicht nur die Arbeit erleichtern. Die Platzierung entscheidet bereits, ob man ein gutes oder schlechtes Layout bekommt, wie viele Lagen notwendig sind, ja sogar ob ein Design überhaupt implementierbar ist. Dabei sind nicht nur die Verbindungen zwischen den Bauteilen zu berücksichtigen (möglichst kurz und kreuzungsarm), sondern auch die Ballouts und die Anordnung der Signale an den Bausteinen. Speziell bei komplexen BGA-Bausteinen kann das Ballout bereits verhindern, dass ein gutes Layout entsteht. Wenn ein Designer dann noch die Orientierung des Bausteins ungünstig wählt, wird die Aufgabe immer schwieriger. Auch die thermische Beeinflussung der Bauteile untereinander ist bei der Platzierung zu berücksichtigen.

1.3. Bus-Priority-Study

Wenn es um Eigenschaften des Routings für High-Speed Signale geht, wird häufig als erster Parameter die Impedanz und Impedanz kontrolliertes Routing genannt. Das ist sicher wichtig, aber nicht der einzige Parameter den man berücksichtigen muss.

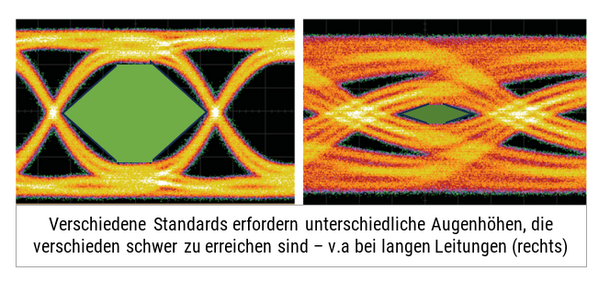

In praktisch jedem Design Guide wird der sehr dehnbare Begriff „route so kurz wie möglich“ verwendet. Aber was ist „so kurz wie möglich“? Es gibt z.B. auch eine minimale Länge zu beachten (z.B. PCIe zu kurz).

Bei Signalen in der Geschwindigkeitsklasse >=10Gb/s kommt es tatsächlich auf jeden Zentimeter Leitungslänge an. Dabei sind besonders die Memory-Interfaces zu berücksichtigen. Dies gilt es bereits beim Platzieren der Bauteile zu berücksichtigen. Hierzu ist eine „Bus-Priority-Study“ notwendig. Es gilt die Signale nach ihrer Priorität zu ordnen. Dabei kommen meist die schnellsten zu erst. Allerdings kann es auch passieren, dass durch bestimmte Rahmenbedingungen ein langsames z.B. IEEE 10GBase-KR Ethernet Signal kritischer ist als ein 16Gb PCIe Gen4 Signal, wenn die 10Gb über lange Leitungen auf einer Backplane verbunden werden, während das PCIe Signal direkt zu einem FPGA auf dem gleichen Board geroutet wird.

Nur nach einer Bewertung der Signale kann man gewichten wie kritisch das Routing eines Signales ist und damit die Bauteilplatzierung optimieren. Auch nach der Bauteilplatzierung ist diese Information wichtig, da man das kürzeste Routing nur erreichen kann, wenn man für die kritischen Leitungen die optimalen Lagen sowie den kürzesten Weg für das Routing verwenden kann. Hierzu ist unter anderem notwendig die Spezifikation der Schnittstellen zu kennen. Während z. B. ein IEEE-Ethernet 10Gb Interface dafür ausgelegt ist „weite“ Wege auf der Leiterplatte zu überbrücken ist ein USB 10Gb Interface für kurze Wege auf der Leiterplatte, aber ein langes Kabel optimiert.

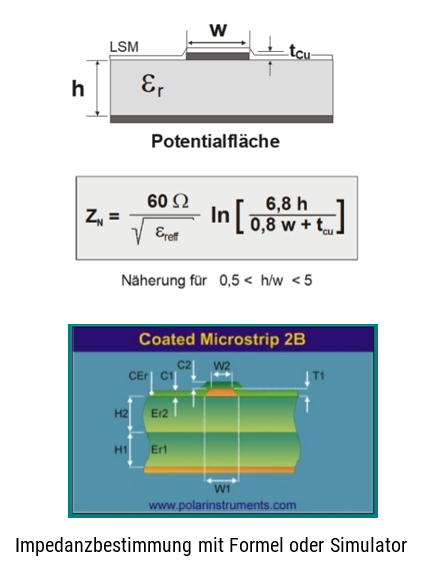

1.4. Impedanzberechnung

Die Leitungsimpedanz ist einer der wichtigsten Parameter für das Routing von High-Speed Signalen. Jeder nicht angepasste Impedanz-Übergang (z.B. an Vias, Steckern) erzeugt Reflexionen. Je besser das Leiterplattenmaterial ist, je geringer die Verluste, umso kritischer werden Reflexionen, da sie nicht mehr gedämpft werden. Dies betrifft nicht nur die Leitungen auf der Leiterplatte, sondern auch die Ausgangstreiber, Stecker, Kabel und Terminierungen.

Bereits zu Beginn des Lagenaufbaus sollten die angestrebten Impedanzen klar definiert sein. Leider liefern viele Tools im Internet, v.a. solche die auf Formeln beruhen, ungenaue Ergebnisse. Die meisten Layout-Programme haben aber einen guten Impedanz-Simulator mit dabei. Meist werden Impedanzen mit einer Genauigkeit von +/- 10% gefordert. Diese 10% beansprucht aber der Leiterplattenhersteller für seine Fertigungstoleranzen. Die berechnete Impedanz sollte daher ziemlich genau der Zielimpedanz treffen. Damit haben verschiedene Leiterplattenhersteller die Möglichkeit durch kleine Anpassungen der Fertigungsdaten (z. B. Leiterbahnbreite) die Ziel-Impedanz zu treffen.

Neben der Berechnung der Impedanz steht oft noch die Frage nach einer „Impedanz kontrollierten Fertigung“ im Raum. Diese stellt sicher, dass auch alle gelieferten Leiterplatten (zumindest alle Panels/Nutzen) getestet werden und innerhalb der geforderten Toleranz liegen. Dies soll verhindern, dass bei einer Serienproduktion das eine oder andere Los außerhalb der Toleranz liegt. Ob ggf. eine Annahme noch akzeptabel ist, muss der Entwickler entscheiden. Der Testcoupon sollte die wichtigste, kritischste Impedanz zur Prüfung beinhalten.

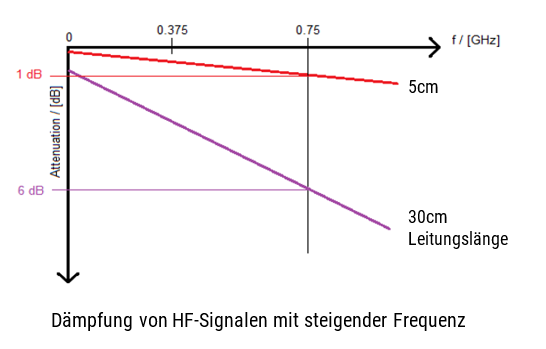

1.5. Verluste und Routing Länge

Die meisten Design Guides definieren Leitungslängen als wichtigen Parameter für den Layouter. Die Leitungslänge ist aber nur eine vereinfachte Sicht auf die Verluste einer Übertragungsleitung. Häufig ist zu den Leitungslängen noch der Verlustfaktor genannt, der angenommen wurde, um die Leitungslänge zu definieren.

Es ist von Vorteil, wenn Designer/Layouter auch Grundkenntnisse zu S-Parametern haben. Dieser Leitfaden setzt dies allerdings nicht voraus. Wichtig wird dies für Signale und Oberwellen im GHz-Bereich. Diese Ansicht im Frequenzbereich zeigt z.B. im sog. Insertion Loss (IL = Einfügungsverluste der Leitung) wie viel Energie man an einem Port in die Leitung einspeist und wieviel Energie nach den Verlusten auf der Leiterplatte an allen anderen Ports ankommt. Also beschreiben S-Parameter nicht nur die Übertragung (IL), sondern auch den Crosstalk (FEXT/NEXT) und Reflexionen (RL = Return Loss).

Die S-Parameter sind die Basis für die Spezifikation der meisten High-Speed Interfaces. So kann man zwar die Längenvorgaben eines Design-Guides einhalten, aber durch schlechte Vias oder Stecker den erlaubten Verlust (Loss) einer Leitung verletzen! Durch eine Betrachtung von Verlusten und der Routinglänge kann man in Verbindung mit der Bus-Priority-Study und der Bauteile-Platzierung vor Layoutbeginn abschätzen, wie kritisch ein Design wird! Der Layouter sollte in der Lage sein, mit geeigneten Simulationstools die zu erwartenden Dämpfungsverluste für verschiedene Layouts zu ermitteln und entsprechend zu berücksichtigen.

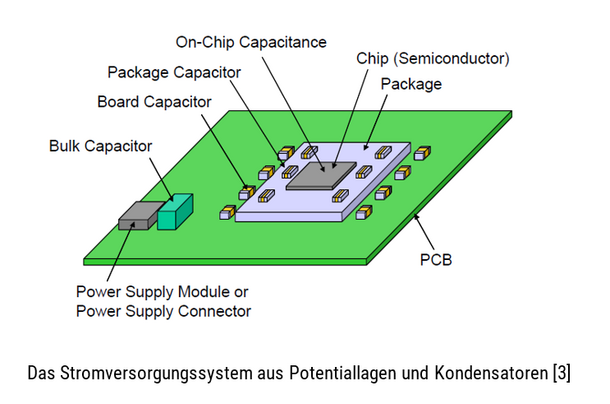

1.6. Stromversorgungssystem (PDN: Power Delivery Network)

Bei der Stromversorgung geht es um mehrere Eigenschaften des Systems und der verwendeten Bauteile. Die einfacheren Eigenschaften sind IR-Drop oder Stromdichte für Gleichstrom (DC). IR-Drop (mit Strom I und Widerstand R) ist die Berechnung des Spannungsabfalls auf einer Potentiallage durch den Kupferwiderstand einer Lage.

Die Ströme auf einer Lage, bzw. in Vias können durch Verengungen einer Versorgungsleitung oder -lage an bestimmten Stellen hohe Stromdichten verursachen, die dann die Leiterplatte lokal erwärmen, was wiederum zu einer Erhöhung des Widerstands vom Kupfer an dieser Stelle führt. Im schlimmsten Falle führt das zum Versagen eines Vias. Der Strom der bislang durch dieses Via geleitet wurde muss dann durch andere Vias fließen, die dann ihrerseits wieder an Ihre Grenzen gelangen...

Schwieriger ist es, die Impedanz des PDN, die die Stromimpulse behindert, richtig zu planen: Während wir bei Signalen von Impedanzen im Bereich von 50…100 Ohm reden, ist es notwendig, bei den Stromversorgungslagen (PDN) Impedanzen im Bereich von wenigen mOhm zu realisieren. Für Frequenzen bis wenige 100MHz werden SMD-Kondensatoren verwendet, um die Impedanzen auf dem PDN zu reduzieren. Diese sind allerdings durch die Induktivitäten begrenzt: Ein Via ist beispielsweise mit einer Anschlussinduktivität von 1nH pro mm (Länge) zu berücksichtigen. Durch geschicktes Anordnen der Vias kann man die Anschlussinduktivität reduzieren. Über die Art und Größen der SMD-Kondensatoren wird in der Industrie oft diskutiert. Die meisten Experten raten zu unterschiedlichen Größen (elektrisch wie mechanisch) um eine niedrige und stabile Impedanz im relevanten Frequenzbereich z. B. bis 400MHz zu garantieren. Werden diese Kondensatoren nicht sehr niederinduktiv (kurze Leitungen) miteinander verbunden, kann dies aber zu unerwünschten Impedanz- und dadurch Resonanz-Peaks führen. Auch hier ist eine Betrachtung im Frequenzbereich (Fourierspektrum) sinnvoll, um das Verhalten der Stromversorgung zu verstehen.

Für hohe Frequenzen oder um Impedanzen im einstelligen mOhm Bereich zu erzielen, werden die Versorgungslagen im Lagenaufbau genutzt und deren Abstand geringgehalten. Sind keine Vollflächen möglich, ist zu beachten, dass bereits die Form einer Stromversorgungsinsel (z.B. ein Cu-gefluteter Bereich) Resonanzen verursachen kann, die sich im Betrieb störend auswirken. Die einfache Regel - „viel hilft viel“- trifft zwar in den meisten Fällen zu: zusätzliche Kondensatoren machen das PDN meist besser. Im ungünstigsten Falle kann aber ein zusätzlicher, falsch platzierter Kondensator unerwünschte Resonanzen verursachen.

Für eine Komplettbetrachtung muss man eigentlich alle Bestandteile des PDN kombinieren, da die einzelnen Teile interagieren. Die niedrigsten Frequenzen werden von den DC-DC Reglern und großen Kapazitäten abgedeckt, sehr hohe Frequenzen vom Decoupling auf dem Baustein-Package und dem Silizium. Die grundlegende Betrachtung der Stromversorgung vor Beginn der Layoutarbeiten vermeidet nachträglich notwendige Änderungen des Lagenaufbaus während des Layouts z.B. wegen fehlender/zu weniger Power Planes!

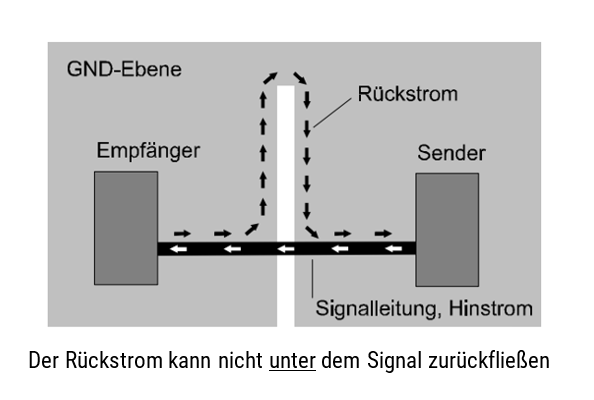

1.7. Design des Rückstrompfads (Current Return Path)

Die Versorgungslagen sind nicht nur für die Stromversorgung der Bauteile zuständig, sondern dienen auch als Rückstrompfad für High-Speed Leitungen. Üblicherweise sind es die GND-Lagen die hier als Rückstromweg dienen. Allerdings kann man durchaus auch VDD-Lagen verwenden, sollte aber berücksichtigen, dass diese i.d.R. etwas schlechter bzw. kritischer sind als vollflächige GND-Lagen.

Hierauf muss der Designer sein spezielles Augenmerk legen, da sich ein schlechtes Design des Rückstrompfades z.B. signifikant auf Crosstalk und Impedanzen auswirkt. Die Fehleranalyse ist bei Problemen im Rückstrompfad sehr schwierig, da das Verhalten der Schaltung schwer vorhersehbar ist. Der Strom braucht einen Rückweg und wird einen Weg finden. Wenn man diesen nicht vorgibt, findet der Strom trotzdem einen Weg, der den Schaltungen (bzw. dem Designer) aber nicht gefallen wird! (Signalverzerrungen und EMV).

Um bei einem Lagenwechsel einen definierten Rückstrompfad zur Verfügung zu stellen werden Rückstrom-Vias (current-return-vias) eingefügt. Hier hängt es wieder vom Interface ab, das man implementiert:

- Langsame Schnittstellen brauchen z. B. nur 1 gemeinsames Rückstrom-Via in 2cm Abstand.

- Schnelle parallele Schnittstellen (z. B. DDR-Memory) brauchen möglichst viele Rückstrom-Vias um den Crosstalk zu minimieren.

- Serielle Schnittstellen sollten ein Rückstrom-Via pro Differential-Pair aufweisen.

- Schnelle, serielle Schnittstellen (> 25Gb) sollten für jedes Signal eines differentiellen Paares ein eigenes Rückstrom-Via aufweisen, dass auch symmetrisch zu den Signal-Vias platziert ist.

Hier kann man sich die Arbeit erleichtern, wenn man bereits vor Beginn der Layoutarbeiten die notwendigen Via Anordnungen vorab definiert.

1.8. Design Guides, Reference Designs, Datenblätter und Spezifikationen

Eine wichtige Informationsquelle sind die Chip Hersteller und Normungsgremien. Hier gibt es von jedem Chip- Hersteller und für alle Themen Design Guides, Reference Designs, Datenblätter und Spezifikationen.

Um zu verstehen worauf es ankommt ist es wichtig, die Spezifikation für die jeweilige Schnittstellen zu kennen. Hierbei geht es nicht nur darum Vorgaben zur Routing-Impedanz, erlaubte Verluste (Losses) auf der Leiterplatte und Implementierungen wie z. B. interleaved vs. non-interleaved routing bei PCIe zu kennen und zu verstehen, sondern auch zu überlegen, ob und wie man die Implementierung im Silizum-Schaltungsdesign Parasitäten im Layout kompensieren kann (Stichwort: Pre-Emphasis, Equalization).

Ähnliche Hintergrundinformationen findet man dann auch in den Datenblättern der Hersteller. Während eine Spezifikation nur die worst case Implementierung vorgibt, sollte man in den Datenblättern die genauen Werte für die verwendeten Chips finden.

Die nächste Quelle für Informationen sind die Design Guides und Applikation Notes (App Notes) der Hersteller. Diese sind meist sehr konservativ verfasst, da ein Chiphersteller kein Risiko eingehen will, dass ein Design nicht funktioniert, obwohl es dem Design Guide gefolgt ist. Den Vorgaben kann man vielleicht in einem „Referenz“ Design folgen, aber für ein produktives Layout muss man häufig von den Vorgaben abweichen. In diesem Fall ist es wichtig zu verstehen, welche Auswirkungen bei einer Verletzung der Vorgaben im Design Guide zu erwarten sind.

Aber selbst bei den Referenz Designs verletzen die Chip Hersteller oftmals die eigenen Design Guides, da es, selbst unter den bestmöglichen Rahmenbedingungen die ein Referenz Design bietet schwer ist, alle Vorgaben vom Design Guide umzusetzen. Außerdem sollte man Referenz Designs auch mit einer gewissen Portion Skepsis entgegentreten. Nur weil es „Referenz“ Design heißt, bedeutet es nicht, dass es auch ein qualitativ hochwertiges Design ist. Im schlimmsten Falle ist das Design gerade so gut, dass man damit ein im Labor lauffähiges Muster bauen kann.

Alle diese Information muss man immer auch mit dem Hintergrundwissen und den Rahmenbedingungen vom eigenen Design betrachten. Nur weil ein Design Guide als Routingvorgabe 50Ohm Routing empfiehlt, bedeutet das nicht, dass 50Ohm die beste Lösung für das eigene Design ist. Abhängig von Stackup, Vias und verfügbarem Platz kann es sein, das 40Ohm oder 60Ohm im eigenen Design bessere Ergebnisse liefern als blind dem Design Guide zu folgen.

Referenz-Designs und Design Guides bieten Orientierung, direkt umgesetzt liefern sie aber fast nie die effektivste Lösung für eine zuverlässig funktionierende Schaltung. Häufig trifft man auch auf widersprüchliche Vorgaben (Constraints) die man mit Hilfe eines Spezialisten bewerten sollte.

1.9. Layout-Studien

Um all die vorangegangen Punkt abschätzen zu können ist es oftmals notwendig vorab eine Layout Studie zu machen. Damit bekommt ein Designer/Layouter eine Vorstellung davon, wie man ein Design unter den eigenen Rahmenbedingungen implementieren kann. Stellt sich dabei heraus, dass man von den Vorgaben im Design Guide abweichen muss, kann man frühzeitig versuchen die Rahmenbedingungen anzupassen oder per Simulation sicherstellen, dass die Abweichungen vom Design Guide keine kritische Verschlechterung der Eigenschaften des Designs mit sich bringen. Dies ist nicht nur in Bezug auf Signal und Power Integrity möglich, sondern gibt auch eine Grundlage für thermische Betrachtungen oder Simulationen, um auch diesen Punkt frühzeitig in die Betrachtung einzubeziehen.