Signal Integrity Simulation: Praktische Anwendung beim PCB Entwurf

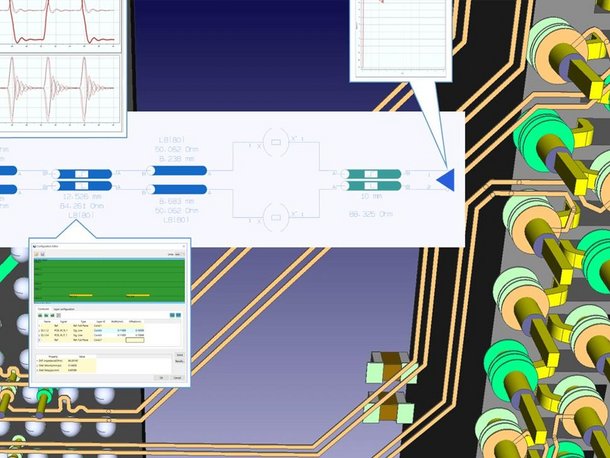

Schnelle Digital-Baugruppen müssen unter Beachtung der Signal- und Powerintegrity entwickelt werden. Allein das Einhalten von Application Notes der Bauteilhersteller führt heute nicht mehr zum Ziel. Schaltung und Leiterplatte müssen entwicklungsbegleitend simuliert werden. Der FED hat zusammen mit CAD-Vendors ein Hands-On-Seminar entwickelt, in dem Sie als Entwickler und Layouter anhand einer Musterschaltung (CPU Baugruppe mit 1GHz Cortex-A9 µC) beispielhaft geschult werden und dabei selbst Hand anlegen und das 10-lagen Board-Layout am CAD-System mit entwerfen und simulieren.

Signal-Integrity Simulation - Praktische Anwendung beim PCB Entwurf

Die steilen Schaltflanken moderner Logikbausteine und der Einsatz moderner Mikrocontroller mit Anbindungen an schnelle Speichersystem sorgen dafür, das selbst Schaltungen mit niedrigen oder moderaten Taktfrequenzen ein High-Speed Designprojekt mit komplexen Anforderungen an die Signalintegrität bedeuten. Entsprechende Simulationswerkzeuge stehen als ergänzende Module zu gängigen EDA PCB Entwicklungsprozesses seit vielen Jahren zur Verfügung, werden aber bisher nicht in der Breite eingesetzt. Dieses Seminar soll fundamentale Informationen über das Themengebiet Signalintegritäts-Simulation im PCB-Entwurfskontext vermitteln.

Anhand einer komplexen Baugruppe mit DDR3 Speichern wird in praktischen Übungen anhand verschiedener kommerzieller Signal-Integrity Simulationswerkzeugen der Einsatz und die Anwendung derartiger Simulationen zur Adressierung von Problemen der Impedanzkontrolle, Signalqualität (Reflexion/Ringing, Crosstalk, Timing) oder der Überprüfung von Designregeln (z.B. DDR3 JEDEC Compliance) durch Simulation erarbeitet.

Anschließend an dieses Seminar findet der zweite Teil Power Integrity Simulation statt. Sie können beide Seminare einzeln oder als Paket buchen.

Themen

Signalintegrität, kurze Übersicht über die Grundlagen

- Herstellervorgaben, Designregeln, Constraints (z.B. JEDEC)

- Leitungstheorie und Impedanz

- Reflexion, Crosstalk, Delay, Flight-Times

- SI Simulation im Zeitbereich und im Frequenzbereich

- Pre-Layoutsimulation/Postlayoutsimulation

Kurz-Einführung in die verwendeten CAD und Simulationstools

Praktische Übungen zur Signal Integrity Simulation (Pre- und Postlayout)

- Datenblätter Vorgaben als Constraints für die Simulation erarbeiten

- Impedanzkontrolle, Impedanzchecks und Impedanz-Experimente

- Simulation DDR3 Interface (Reflexionen, Timing, Eye-Diagramme)

- Topologie- und Terminierungs-Experimente

- Übersprechen/Crosstalk

Zielgruppe

Das Seminar richtet sich an Schaltungsentwickler und PCB-Layouter. Der Umgang mit CAD Werkzeugen sowie Grundkenntnisse im High-Speed Design sind hilfreich, aber nicht Voraussetzung.

Referent

Ralf Brüning

Ralf Brüning ist als Produkt Manager und Senior Consultant am Zuken EMC Technology Center in Paderborn mit verantwortlich für die Konzeption und Weiterentwicklung von High-Speed Design- und EMV-Analyse-Werkzeuge (Schwerpunkt Signal- und Power-Integrity). Er ist regelmäßiger Sprecher auf nationalen und internationalen Technologiekonferenzen und -Kongressen. Er beschäftigt sich seit mehr als 30 Jahren mit Elektronik Design Automation (EDA), zuerst bei der Nixdorf Computer AG in den Bereichen Logik-Simulation und Leiterplatten-Fertigungsprozesse, anschließend im EDA-Forschungslabor CADLAB und in der INCASES Engineering GmbH. Nach der Übernahme von INCASES durch Zuken im Jahre 2000 arbeitete er in den letzten Jahren an der Konzeption der Zuken Simulationswerkzeuge entscheidend mit.