FED-Panel digitaler Lötstopplack lotet die neuen Designfreiheiten aus

Elf Experten aus ganz Europa reisen zum FED-Panel „digitaler Lötstopplack“ zur 30. FED-Konferenz nach Potsdam. Die Expertenrunde moderieren FED-Vorstand Michael Schleicher und der Prozessexperte Luca Gautero, Suess Microtec, am 29. September in englischer Sprache.

„Der Panel digitaler Lötstopplack soll ein Schlaglicht auf das Thema in der Designer- und Entwickler Community werfen und die neuen Möglichkeiten bzw. Designfreiheiten beim Leiterplattenentwurf darstellen“, sagt Initiator Michael Schleicher, Leiterplattenlayouter in der Entwicklung Automotive Systems, Hardware Layout & Service bei Semikron. Für viele Designer sei das Thema noch neu. Dabei liegt es voll auf der Höhe der Zeit: weniger Prozessschritte, geringerer Materialverbrauch, bessere CO2-Bilanz.

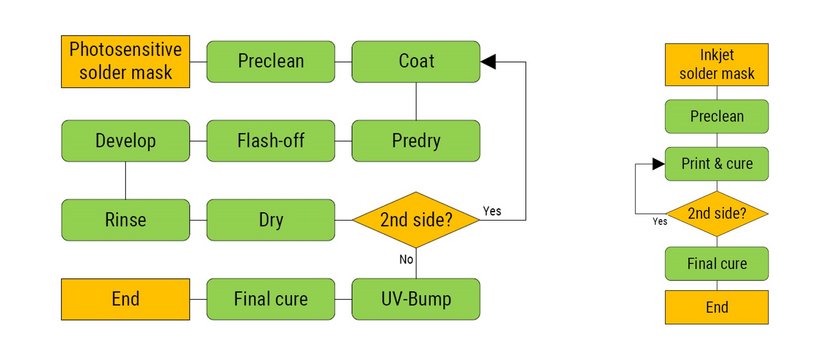

Beim herkömmlichen Aufbringen der Lötstoppmaske wird die gereinigte Leiterplatte oftmals durch einen Gießvorhang aus Lötstopplack geschoben. Je nach Geschwindigkeit und Viskosität verbleibt ein dünner Lackfilm auf der Oberfläche. Danach wird der Lack belichtet und an den Stellen, an welchen er nicht erforderlich ist, z.B. die Bauteileanschlüsse, wieder entfernt. Für eine dickere Lötstoppmaske kann die Leiterplatte den Prozess bis zu drei Mal durchlaufen. Zum Ende des Prozesses wird das Epoxidharz vollständig ausgehärtet und bildet den widerstandsfähigen, permanenten Schutz für das Leiterbild.

Im Gegensatz zum herkömmlichen Prozess ist der digitale Lötstopplack ein additives Lötmasken-Tintenstrahldruckverfahren. Das heißt, es wird nur die erforderliche Lackmenge an den jeweiligen Stellen der Leiterplatte aufgebracht (drop on demand). Der Belichtungs- und Spülprozess entfällt, was die Produktion beschleunigt. Hinzu kommt: weil nicht mehr die gesamte Oberfläche mit Lötstopplack geflutet wird, reduziert sich der Materialverbrauch um bis zu 80 Prozent. Die digitale Lötmaske ist konform für Anforderungen nach IPC-SM-840 für Klasse H & T; Brennbarkeit nach UL-94V0, konform nach REACH, halogenfrei und NASA Outgassing (NASA spec: SP-R-0022A). Der saubere „Andruck“ an den Lötstellen verhindert ionische Verunreinigungen und die definierte Kantenabdeckung entspricht den Anforderungen von Automotive und Bahntechnik.

Bei unterschiedlichen Schichtdicken ist der Nutzen am größten

Grundsätzlich kann mit den üblichen Lötstopplackdaten eine Leiterplatte digital beschichtet werden. „Doch der größte Nutzen ergibt sich, wenn bestimmte Bereiche auf der Leiterplatte unterschiedlich dünn oder dick beschichtet werden müssen“, erklärt der Experte. Ein Beispiel ist eine sehr dünne Lackschicht am µBGA und an einer anderen Stelle eine sehr dicke Schicht, um die Kanten der Kupferstrukturen vollständig abzudecken oder bei Hochspannung an einem Übertrager aufgrund der galvanischen Trennung. Die unterschiedlichen Schichtdicken sind in einem Durchlauf möglich.

Das Engagement des FED für das Thema digitaler Lötstopplack kommt nicht von ungefähr. Der FED-Arbeitskreis 3D-Elektronik hat es seit Jahren auf dem Radar. Zur der FED Konferenz 2019 in Bremen wurde Joost Valeton, Meyer Burger, eingeladen, um den Prozess im Vortrag „Inkjet Printing for Solder Mask on PCB” vorzustellen. 2020 gab Jürgen Wolf, Würth Elektronik, in einem Webinar einen „Überblick zur Lötstoppmaske in digitaler Additivtechnik bis hin zur funktionellen 3D Oberfläche“. Die Aufzeichnung gibt es im Youtube-Kanal des FED. Und auf der FED Konferenz 2021 in Bamberg hat Michael Schleicher in seinem Vortrag „Disruptiver Ansatz additiv hergestellter Schaltungsträger“ die Chancen der neuen Fertigungsprozesse herausgearbeitet.

Nun folgt der FED-Panel, zu dem Mitinitiator und Moderator Michael Schleicher elf Experten eingeladen hat, die den gesamten Prozess repräsentieren: PreTretment (Oberflächen) und Equipment-Hersteller, Tintenhersteller, Maschinenbauer, Leiterplattenfertiger, die Inkjet bereits einsetzen und EDA-Tool-Spezialisten. Co-Moderator ist der Prozessexperte Luca Gautero von Suess Microtec „Das bietet uns die Möglichkeit, die ganze Lieferkette zu betrachten vom Design bis zur fertigen Leiterplatte“, betont Luca Gautero. Dabei sollen alle Fragen beantwortet und die Vorteile für die Nutzer aufgezeigt werden.

„Ich war überrascht und natürlich erfreut über das Echo. Alle angefragten Firmen haben der Teilnahme zugestimmt und begrüßt, dass sich jemand im deutschsprachigen Raum an dieses komplexe Thema traut“, betont Luca Gautero. „Ein FED-Panel ist ein passendes und neutrales Format“, fügt Michael Schleicher hinzu. Ebenso sei aus den Vorgesprächen herausgeklungen: Der Impuls, das Verfahren zu nutzen, muss von den Anwendern ausgehen. Der FED erreicht die Designer und dafür ist er da: Vernetzen, Weiterbilden, Wissen managen.

Prozessfragen beantworten und Handlungsfelder für das Design sichtbar machen

Durch die Moderation im neutralen Panel haben alle Beteiligten die Chance, die gestellten Fragen zu beantworten und zu kommentieren. Die beiden Moderatoren sind davon überzeugt, dass der Erfolg auch davon abhängt, wie gut sich Designer oder Baugruppenentwickler auf das Thema einlassen, um die Vorteile der Technologie zu erkennen und diese im nächsten, geeigneten Projekt, implementieren. Heißt, die Technik hat dann Erfolg, wenn in die Produktentwicklung auch überzeugt ist.

Für Michael Schleicher geht es noch weiter. Aus dem Panel heraus, gilt es, Hilfestellungen und Lösungen für die Designer und Entwickler zu erarbeiten. „Wir erfahren, wo es eventuell noch technische Fragen oder Wissenslücken gibt und werden ein Gap-Analyse vornehmen in Richtung PCB-Design und Datenformate und diese in Arbeitsgruppen, den FED-Arbeitskreisen (AK) Leiterplatte, Design & Baugruppe, 3D-Elektronik und Normen einbringen.“