ZED Level I - Grundlagenkurs Leiterplattendesign

Der Kurs ZED Level I ist die erste Stufe der Ausbildung zum Zertifizierten Elektronik-Designer. Er vermittelt die Grundlagen des Leiterplattendesigns von der Idee bis zur fertigen Baugruppe.

Anhand eines Schulungsprojektes werden theoretische Kenntnisse vermittelt und in Übungen mit einer handelsüblichen CAD-Software umgesetzt. Bei je einem Leiterplattenhersteller und Baugruppenfertiger vor Ort durchlaufen die Teilnehmer den kompletten Herstellungsprozess einer Leiterplatte inklusive Bestückung und Prüfung. Jeder Teilnehmer erhält nach dem 2-wöchigen Kurs eine funktionierende Baugrup-pe und praxisnahe Schulungsunterlagen, die er im beruflichen Alltag als Nachschlagewerk verwenden kann. Der Kurs gliedert sich in zwei Teile mit je fünf Schulungstagen.

Dauer

2 x 5 Tage

Termine 2024

Termine 2025

1. Termin

Teil 1: 03.-07.03.2025

Teil 2: 31.03.-04.04.2025

2. Termin

Teil 1: 02.-06.06.2025

Teil 2: 30.06.-04.07.2025

3. Termin

Teil 1: 13.-17.10.2025

Teil 2: 03.-07.11.2025

Themen

Teil 1 (1. Woche)

Modul 1 - 4

- Einführung Leiterplatte, Designprozess

- Einführung Schaltplan Theorie

- Begriffe / Elektrotechnik

- Einführung in die Arbeit mit der CAD-Sofware mit Praxis

Modul 5 - 8

- Praxis: Schaltplan im CAD erfassen

- Einführung Bauteile-Bibliotheken

- Praxis: CAD-Umsetzung

- Einführung 3D-Darstellung + Praxis Umsetzung

Modul 9 - 12

- Projekt eröffnen, Leiterplattendefinitionen, 2 Lagen, Platzierung mit THT-Bauteilen, Routing

- Praxisumsetzung

- Design Rules (DRC), Verbesserungen

- Praxis: CAD-Umsetzung Fertigungsdaten mit Gerber erstellen

Modul 13 - 16

- Dokumentation für die Fertigung erstellen und Änderungsdurchlauf mit Praxis

- Vertiefungen, Vermeidung von Inseln und Antennen, Kupferflächen, Wärmefallen, Lötstopp, Baugruppentest, Design-Rules

Modul 17 - 19

- Zusammenfassung, Gruppenarbeit

- Abschlussprüfung Teil 1

- Auswertung

Optional

- Bestimmung der Design-Rules bis zum fertigen Design

Teil 2 (2. Woche)

Modul 21 - 24

- Leiterplattendesign: 4 Lagen, Platzierung mit SMD Bauteilen, Praxis: CAD-Umsetzung Routing

- Design Erweiterung und Vertiefung

- Optional: Zusatzprojekt Interposer (aus der Praxis) und Praxis: CAD-Umsetzung

Modul 25 - 28

- Begrifferklärung EMV, Impedanz, Signalintegrität

- Praxis: Fehlererkennung im Schulungsprojekt

- Qualitäts-Technik 1: Spezifikation, Design, Zuverlässigkeit, Richtlinien, Produktprozess

- Qualitäts-Technik 2: Leiterplatte, Baugruppen, Qualifikation (Klima, Mechanik)

Modul 29 - 32

- Vorbereitung zum Besuch Leiterplattenfertigung, Arbeitsvorbereitung, CAM

- Fertigung und deren Maschinenpark

- Praxis: Besichtigung einer Leiterplattenfertigung, Arbeitsvorbereitung, CAM, Fertigungsprozesse

Modul 33 - 36

- Vorbereitung zum Besuch Baugruppenfertigung, ESD, Arbeitsvorbereitung, Löten, Fertigungsprozesse, -technologien, -prüfungen, Reparaturen, Reinigung, Lackieren, Vergießen, Environmental Stress Screening

- Praxis: Besichtigung einer Baugruppenfertigung, Arbeitsvorbereitung, Fertigungsprozesse

Modul 37- 39

- Zusammenfassung, Gruppenarbeit

- Abschlussprüfung Teil 2

- Auswertung

Zielgruppe

Der Kurs richtet sich an Neueinsteiger und Hardware-Entwickler, die praxisnah, zeitoptimiert und berufsbegleitend das Leiterplattendesign erlernen wollen. Die zukünftigen Designer benötigen Basiswissen der Elektrotechnik, der Fertigungstechnologie, sowie in der Materialkunde um die komplexen Zusammenhänge im Designprozess zu verstehen.

Weiterbildung für Berufsanfänger und Studienabsolventen

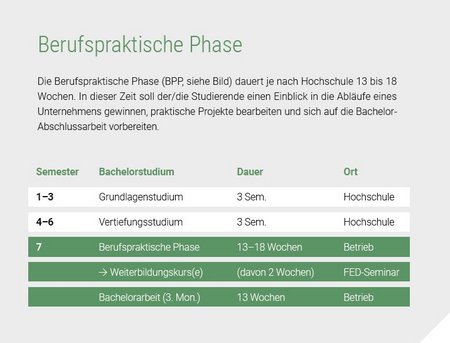

Junge Ingenieure und Ingenieurinnen für ein Unternehmen zu gewinnen, wird immer schwieriger. Gute Absolventen und finden ihren Job meist bereits zum Ende des Studiums in der Berufspraktischen Phase. In dieser Zeit sammeln Studierende Praxiserfahrung in Unternehmen.

Unser Angebot:

Wir bieten Unternehmen an, Berufsanfänger und Studierende in der Praxisphase in einem 2-wöchigen Grundlagenkurs im Leiterplatten und Baugruppen-Design zu schulen. Dieser Kurs umfasst unter anderem Module zu Bauteilen, Leiterplatten-Design und ein praktisches Training an einem CAD-System.

Für Studierende in der Berufspraktischen Phase gewähren wir einen Rabatt von 20% auf die Teilnahmegebühr. Bitte teilen Sie uns dies bei Anmeldung mit.

Vorteile für Unternehmen:

- Sie schaffen einen Anreiz für Studierende und erhöhen die Chance, diese für Ihr Unternehmen zu gewinnen.

- Berufsanfänger oder Studierende können nach der Schulung qualifiziert in der Entwicklung eingesetzt werden.

- Berufsanfänger und Studierende erhalten frühzeitig Basiswissen im Schaltungsentwurf und Leiterplattendesign, das nicht erst später im Berufsalltag vermittelt werden muss.

Referenten

Erika Reel

Mitglied des FED-Vorstands und verantworlich für den Bereich Design im FED. Nach 7-jähriger Tätigkeit als PCB Layouterin bei ABB in Turgi war Erika Reel 22 Jahre bei der Firma Omnisec AG in Dällikon, Schweiz, tätig. In der Entwicklung der hochzuverlässigen Nachrichtentechnik hat sie 10 Jahre die Elektronikkonstruktion und 10 weitere Jahre die Elektronik und Mechanikkonstruktion geleitet.

Dieter Wachter

Dieter Wachter ist seit 1986 Entwicklungsingenieur bei Diehl BGT Defence in Überlingen und beschäftigt sich mit dem Design von Leiterplatten und Hybriden. Als Gruppenleiter berät und unterstützt er Entwickler bei der Aufbau- und Verbindungstechnik. Dieter Wachter wurde ausgezeichnet mit dem 1. Preis des Veribest PCB-Design-Wettbewerbs 1999 und dem EDA-Vendor PCB-Design-Award 2002 (heute: Mentor Leadership Award).

Schulungszeiten

Der Kurs besteht aus 2 Teilen mit je 5 Schulungstagen (Mo-Fr)

Schulungszeiten

Mo 08:30 - 16:30 Uhr

Di 08:30 - 17:00 Uhr

Mi 08:30 - 17:00Uhr

Do 08:30 - 17:00 Uhr

Fr 08:00 - 15:00 Uhr

Bedingungen

Die Kursgebühren gelten für den kompletten 2-teiligen Grundlagenkurs Leiterplattendesign Theorie & Praxis (2 x 5-tägige Schulung).

Enthaltene Leistungen

Schulungsunterlagen, fertige Baugruppe (Schulungsprojekt), Benutzung Schulungslaptop (CAD-Software: Pulsonix), ZED Level I Prüfungen Teil 1 und 2, ZED Level I Abschlusszertifikat, 10 x Mittagessen, Kaffeepausen sowie alkoholfreie Pausengetränke.

Die Teilnehmerzahl ist auf 14 Personen pro Kurs begrenzt.

Nach Eingang Ihrer Anmeldung erhalten Sie als Bestätigung der Teilnahme eine Rechnung mit dem Zahlbetrag. Der Kostenbeitrag ist vor Veranstaltungsbeginn an den FED zu überweisen. Bitte zahlen Sie erst nach Erhalt der Rechnung.

Bei Stornierung der Anmeldung zwischen 28 und 14 Tagen vor Seminar-/Kursbeginn (nur schriftlich per Post, E-Mail oder Telefax möglich – es gilt der Posteingangsstempel) wird eine Stornogebühr in Höhe von 30 % des Gesamtrechnungsbetrages erhoben. Danach ist in jedem Fall der volle Betrag zu zahlen. Bei Nichterscheinen oder verspäteter Abmeldung besteht kein Anspruch auf Rückerstattung der Teilnahmegebühr.

Der Veranstalter behält sich das Recht vor, den Seminartermin auch nach erfolgter Anmeldebestätigung unter Rückerstattung der Gebühren abzusagen.

Mindestteilnehmerzahl: 8.

Die Schulungen werden in Deutsch gehalten.

Prüfung

Teil 1 und 2 des Kurses schließen jeweils mit einer Prüfung ab. Nach Bestehen der Prüfungen erlangen die Teilnehmer den Abschluss Zertifizierter Elektronik-Designer ZED Level I.

Damit erlangen die Teilnehmer die erste Stufe einer anerkannten beruflichen Qualifikation, die ihnen eine optimale Ausgangsposition für die Karriere in einer Branche mit Zukunft gewährt.

Mehr zum Schulungsprogramm "Zertifizierter Elektronik-Designer (ZED)"...