## Bericht des Treffens der Regionalgruppe Stuttgart in Achern am 22.06.2017

Im Rahmen der Rundreise traf sich die FED Regionalgruppe Stuttgart in Achern bei Firma Fritsch Elektronik GmbH.

Für dieses Treffen hatten wir uns den bisher heißesten Tag des Jahres ausgesucht und es war sehr positiv, dass unser Gastgeber mit kalten Getränken und Eis am Stiel für ein wenig Abkühlung gesorgt hat, vielen Dank dafür.

Frau Bromberger, kaufmännische Geschäftsführerin und Herr Sester, technischer Geschäftsführer begrüßten die Teilnehmer und stellten das Unternehmen vor. Direkt im Anschluss wurde die Betriebsführung durchgeführt. Fritsch Elektronik verfügt über 4 vollautomatische SMT Bestückungslinien und ist damit in der Lage Großserien, als auch sehr flexible Prototypen zu fertigen. Hierbei liegt der Schwerpunkt auf Industrie – Elektronik. Abgerundet wird die Fertigung durch THT Bestückung, eine moderne Selektivlötanlage, ein flexibles Prüffeld sowie die Möglichkeit für Schutzlackierung und Verguss der Baugruppen.

Die Fachthemen richteten sich speziell an CAD Designer. Wie kann man bei der Erstellung des Layouts "Unzulänglichkeiten" vermeiden und so die Fertigung der Leiterplatten deutlich sicherer machen.

Geschäftsführer Firma Fritsch Frau Bromberger Herr Sester

Referent Karl-Heinz Kluwetasch CSK-Cad Systeme

Referent Günther Schindler EASYLOGIX

Regionalgruppenleiter Roland Schönholz Michael Matthes

# 1. Fachvortrag: Systemunabhängige Erstellung von SMD Anschlussflächen nach IPC 7351 Referent: Karl-Heinz Kluwetasch, Firma CSK - CAD Systeme Kluwetasch

Die fortschreitende Internationalisierung der Firmen erfordert eine weitgehende fertigungs-unabhängige Erstellung der PCB-Designs nach international standardisierten Vorgaben.

Die kontinuierliche Größenreduzierung der Bauteile verlangt dabei nach immer genaueren Berechnungen der Anschlussflächen für aktive und passive Bauteile für die unterschiedlichsten Anwendungen im Bereich der Consumer-Elektronik oder im Mobilfunkbereich. Die IPC-7351B, die Version C ist noch nicht freigegeben, "Generic Requirements for Land Pattern-Guidelines" deutsche Übersetzung vom FED, definiert die dazu notwendigen Anforderungen an die Pads. Erweiterungen in der IPC-7351C beinhalten unter anderem die Einführung eines "Proportional Pad" für Bauteile. An dieser Stelle weist der Referent noch einmal darauf hin, dass die IPC-Dokumente nur Richtlinien sind.

Auf die unterschiedlichen Bezeichnungen der Lötflächen und deren vielfältige Formen wird hingewiesen. Ein Standardformat ist nicht vorhanden bedingt durch die zahlreichen Bauteilehersteller und CAD-Systeme. Durch das häufige Hinzukommen neuer Bauteile, hauptsächlich THT-Bauteile ist die Version C noch nicht veröffentlicht worden. Um hier eine einfache Berechnungsgrundlage zu schaffen ist die PCB-Library-Expert-Software erstellt worden. In der Version B mit dem inkrementalen Referenz-Kalkulator, die Version C wird auch den proportionalen Referenz-Kalkulator enthalten.

Eingebunden in die Library-Expert-Software sind Benutzer- und Firmenspezifische Einstellungen und Vorgaben und die Dimensionen von zahlreichen Bauteilen. Es besteht die Möglichkeit die Ausgabe der PCB-Designs dann in den verschiedenen führenden CAD-Formaten und notwendige Dokumentationen als Ausgabeergebnis zu erhalten. Der Unterschied zwischen inkrementalen und proportionalen Berechnungen der Pads wird an Hand eines Pad-Stacks eines THT-Bauteiles verdeutlicht. Je nach Designstruktur und Lötprozess sind für die Toleranzbetrachtung drei unterschiedliche Anschlussflächengrößen, Maximum, Median und Minimum, entwickelt worden. Es können jedoch Variationen der Padgrößen in vielen Fällen notwendig sein. Toleranzbetrachtungen sind jedoch ein wesentlicher Faktor. Für die unterschiedlichen Anschlussflächen der Bauteile werden abgerundete Pads empfohlen. Besonders für HF-Design sind rechteckige Pads nicht geeignet. Weiterhin werden Richtlinien empfohlen für

- Zeichnungselemente,

- Linienbreiten der Bauteil-Kontur, wobei hier Unterschiede zwischen den drei Einstufungen Maximum, Median und Minimum zu beachten sind,

- Kennzeichnung der Außenkontur des Bauteiles mit seinen Anschlussflächen, in der Version B als Rechteck in der Version C dem Bauteil angepasst

- Polaritätskennzeichnungen

- Bauteilbezeichnungen

- Festlegung des Nullpunktes, normalerweise im Flächenmittelpunkt, bei unregelmäßigen Bauformen wird er Anschluss 1 herangezogen. Hierbei ist Level A und B zu beachten. Level A Anschluss 1 in der linken oberen Ecke, Level B in der Linken unteren Ecke.

- Größe der Passermarken nach dem 3-Stufigen Konzept

Die umfangreichen Erweiterungen der Namenskonvention für Padstacks sorgen für die eindeutige Bezeichnung der Pads auf den Außenlagen. Zur nachfolgenden Standarddefinition

#### Pad Stack Standard Definition

- Die Lötstoppmaske ist im Maßstab 1:1 der Pad-Größe

- Die Pastenmaske ist im Maßstab 1:1 der Pad-Größe

- Auf den Innenlagen ist die gleiche Pad-Form, wie auf den Außenlagen

- Die primären und sekundären Pads haben die gleiche Größe

- Auf den Innenlagen sind die Pad-Formen rund

- · Vias (Durchkontaktierungen) sind rund

- · Montagebohrungen sind rund

- Unzulässige Zeichen: "", ; : / \ [] () . {} \* & % \$ # ! @ ^ =

- · Wärmefallen haben 4 Anschlussstege

- Wärmefallen: Gleiche Größe beim Außendurchmesser (OD) und der Plane-Freistellung

- Proportionales Verhältnis: Pad-Freistellung (Anti-Pad) in einer Plane zum Pad

- Proportionales Verhältnis: Wärmefallen-Innendurchmesser (ID), Außendurchmesser

Quelle. Vortragsfolien Karl. Heinz Kluwetasch CSK

sind weitere besondere Vorgaben für Padstacks vorgegeben um diesen in allen Leiterplattenlagen zu beschreiben. Mit Beispielen wird diese Bezeichnung verdeutlicht. Weitere neue Erweiterungen der Landpatter-Namen

- Pinzahl und Pitch-Abstand am Anfang des Namens

- Jeder Bibliotheks-Name wird mit der Herstellerfirma und der Artikelnummer oder Gehäusebezeichnung verknüpft

gewährleisten die eindeutige Vergabe des Namens.

Ein Ausblick auf die Lötempfehlungen in der Version C für Gull Wing Anschlüse und Chip-Bauteile wird auf einigen Folien gegeben. Ein Vergleich der Vorgaben in der IPC-7351C und der proportionalen Berechnung von Lötflächen zeigt die deutliche Minimierung der für die heutigen komplexen und dichten Strukturen auf der Leiterplatte notwendig ist. Mit der Software PCB Library Expert lassen sich IPC-7351C konforme Bauteil-Anschlussflächen mühelos erstellen und das inklusive der Informationen aus den jeweiligen Bauteildatenblättern. Die Funktionalität der Software wurde im Vortrag erklärt und an aktuellen Praxisbeispielen präsentiert.

Blick in die Teilnehmerrunde

# 2. Fachvortrag: Softwarehilfe für die Erhöhung der Qualität in der Leiterplattenfertigung Referent: Günther Schindler, EASYLOGIX

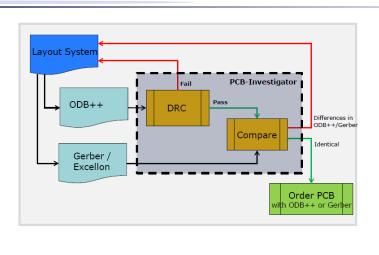

Für eine hohe Qualitätsgüte in der Fertigung von Leiterplatten und Baugruppen müssen die zur Verfügung stehenden Datensätze ein vollständiges Abbild darstellen. Um diesen Anforderungen gerecht zu werden, hat die Firma EASYLOGIX, wie Günther Schindler ausführt, entsprechende Konvertierungsprogramme entwickelt.

- PCB-Investigator –Konvertierung der Formate der verschiedenen CAD-Systeme zur Prüfung der Daten vor der Übergabe an die Fertigung

- Native Board Import Konvertierung von 3D-Formaten

- Pane Optimizer Herstellerorientierte Ausnutzung der Fertigungspanel

- PCB I Physics Analyse und Überwachung des Thermomanagements auf der Leiterplatte.

Im Nachfolgenden wird hauptsächlich der PCB-Investigator betrachtet. Ein umfassendes Datenformat ist ODB++, welches von den namhaften CAD-Systemen ausgegeben werden kann. IPC-2581 und GenCad 1.4 kann mit dem Investigator konvertiert werden. ODB++ beinhaltet im Datensatz den Lagenaufbau über die Stückliste bis zur Netzliste die komplette Struktur der Leiterplatte. Gerade der Lagenaufbau ist für die Fertigung ein wesentlicher Faktor in Bezug auf Stromtragfähigkeit, Impedanz und vieles mehr. Schwachstellen können durch einfache Prüfroutinen rechtzeitig erkannt werden und dem Leiterplattenhersteller werden eindeutige Unterlagen zur Verfügung gestellt. Auch für eine Angebotserstellung stehen komplette Unterlagen zur Verfügung. Der mögliche Import- Export der verschiedenen Datenformate wird auf einer Tabelle dargestellt und einige wichtige Datenformate betrachtet.

- ODB++ ist das Hauptformat des PCB-Investigators und gewährleistet einen optimalen Austausch der Daten zwischen der Entwicklung und der Fertigung, wegen seiner eindeutigen Definition der Informationen und der Möglichkeit der Fehlerentdeckung während der Konvertierung.

- DFX-Format ist ein weitverbreitetes Format für den Austausch von CAD-Daten. Da das Format normalerweise dimensionslos ist, muss bei der Erstellung von Zeichnungen ein Viewer verwendet werden.

- GenCad ist ein spezielles Format für die Leiterplattenherstellung und –prüfung, umfasst jedoch von der Netzliste bis zur Lagenaufbau alle notwendigen Daten. Es gehört mit ODB++ zu den wichtigsten Datenformaten.

• Das Gerberformat ist ein Standardfile im ASCII-Format und gestattet dadurch einen einfachen Austausch zwischen der Entwicklung und der Produktion.

Besonders zu beachten bei der Konvertierung sind die Nachkommastellen. Die entstehende Zahl ist nur einen Annäherung an die reelle Zahl. Durch Rundungen bei mehreren Konvertierungen und Wechsel zwischen metrischen und angloamerikanischen Einheiten können Unterschiede im µm-Bereich entstehen, die bei den heutigen engen Strukturen zu Problemen führen können. Verdeutlicht wird es, wenn eine Linie bei der Anfang und Endpunkt sich in der 6. Nachkommastelle unterscheiden und diese Daten in Gerber konvertiert. Vor der Konvertierung ist es ein Punkt, danach nach Gerberauslegung jedoch ein Kreis. Fehler sind damit vorbestimmt. An Hand von Folien werden mit weiteren Beispielen die entstehenden Übertragungsfehler durch die Konvertierung aufgezeigt (Lagen passen nicht übereinander, Stopplackfehler entstehen, Anbindungen sind nicht 100%ig).

Im Gegensatz zu einer ANSYS-Analyse über die Temperaturverteilung wendet EASYLOGIX hier ein 2D-Verfahren an, das eine große Zeitersparnis zur Folge hat. Die Verlustleistung der Bauelemente wird aufgenommen und ein Strom kann eingeprägt werden. Über die Wärmeflächen können die Hotspots erkannt werden und ein 3D-Modell erleichtert die Erkennung des Problems. Vergleiche von Lagenaufbauten, Stücklisten und Netzlisten vervollständigen die Möglichkeiten einer kompletten Überprüfung. So entsteht ein kompletter Flow über alle möglichen Strukturen im Aufbau der Leiterplatte und damit die Gewährleistung überprüfter Daten an die Fertigung.

### **Review Prozess**

Quelle: Vortragsfolien Günther Schindler, EASYLOGIX

EASYLOGIX.DE

Die Vorträge von Karl-Heinz Kluwetasch (CSK-CAD Systeme Kluwetasch) und Günther Schindler (EASYLOGIX) können von der FED Homepage heruntergeladen werden.

Ein besonderer Dank geht nochmals an Firma Fritsch Elektronik und Frau Hänßler für die perfekte Organisation vor und während des Regionalgruppentreffens.

Roland Schönholz

FED Regionalgruppenleiter RG Stuttgart